Introdução Ao RISC-V

O que é o RISC-V? Sabe-se que para desenvolver um CPU requer experiência ao design em várias especialidades:

- Eletrônica Digital;

- Compiladores;

- e Sistemas Operacionais.

Quando um projeto é baseado de uma série de projetos acadêmicos de design de computadores tem-se então um projeto que abrange vários requisitos. Ele foi desenvolvido por profissionais e voluntários entusiastas e com isso obtêm-se como resultado um moderno e de alta qualidade conjunto de instruções para computador de propósito geral, o RISC-V.

Para projetar tal ISA, os autores possuíam vasta experiência em pesquisa na área além de simulação e validação dos design do projeto, assim, RISC-V é um novo conjunto de instruções de arquitetura com propósito geral.

Produzido pelo Computer Science Divison na Universidade da Califórnia, Berkeley, é um Instruction-Set Architecture (ISA) open-source (BSD). É um conjunto limpo, modular com inteiros bases em 32, 64 e 128 bits e várias opções de extensão de instruções como ponto-flutuante, multiplicadores, etc. Cada usuário demanda que os designers considerem a performance e eficiência energética quando projetar processador e o RISC-V é um conjunto de fácil implementação comparado a outras alternativas e o projeto possui grande aceitação na indústria de semicondutores.

Objetivo Do RISC-V

Sua meta é criar um conjunto de instruções ‘universal’ que é livre e aberto para todos os usuários, provendo tudo que é necessário para suportar perfeitamente qualquer projeto comercial, incluindo fazer design, fabricar e vender os chips e software RISC-V.

Não é o primeiro projeto desse porte e open-source a aparecer, mas seu projeto é modelado para ser útil nos dispositivos computacionais mais modernos que vão desde servidores, celulares high-end até projetos embarcados de pequeno porte. Em contraste disso, chips da ARM e MIPS Technologies necessitam de licença para uso de suas patentes e também requerem acordos de confidencialidade para uso de seus documentos que citam as vantagens de seus design e conjunto de instruções.

O ISA RISC-V tem sido desenvolvido com o mais pequeno, rápido e mínimo gasto de energia de implementações existente hoje e sem sobrecarregar outras partes do seu sistema.

Exemplificação

Consideremos um smartphone moderno que possui possui dúzias de cores com diferentes pilhas de softwares, por exemplo:

- Uma aplicação ARM no CPU;

- Uma GPU;

- 3 à 5 DSP;

- Um core de gerenciamento de energia.

Em teoria, todos usam uma variante de um ISA simples e muitos casos, reutilizando hardware e software. RISC-V poderia oferecer uma opção prática para unificar todos esses cores 8num único local.

Propósito De Uso Do RISC-V

Seu propósito de mercado é amplo ao ponto de ser suportado para executar em: 1) Microcontroladores que processem imagens, gráficos; ou até mesmo 2) Processadores de servidores.

Assim, o ISA deve ser consistente em microarquiteturas. É direcionado para ser adequado para quase todo tipo de implementação desde design Scalar in-order até design out-of-order e similarmente, é projetado para ser adequado a quase todas implementações. Desde macros sintetizações em FPGA até projetos totalmente customizados.

Por causa do crescente interesse em aceleração em processamento, extensibilidade do RISC-V é parte essencial da universalidade, podendo adicionar módulos, temos uma arquitetura que atende a todos os projetos de hardware. Para ativar as extensões, porções do espaço de codificação de instruções já foram reservados para uso futuro.

RISC-V provê garantia de funcionamento para instruções de inteiros tamanho 32, 64 e 128 bits e uma família de extensões opcionais/predefinidas. Embora alguns processadores disponíveis hoje no mercado sejam amplamente utilizados, eles são complexos e é difícil de ser utilizado para experimentação e uso acadêmico. Com isso, tendo construído uma arquitetura simples e clara, tem-se então implementações finais simplificadas.

Design Do RISC-V

Termos Gerais

RISC-V possui 32 registradores inteiros, e 32 registradores opcionais para ponto flutuante. Também existe uma variante RISC-V com 16 registradores inteiro e sua memória possui endereçamento de 1 byte.

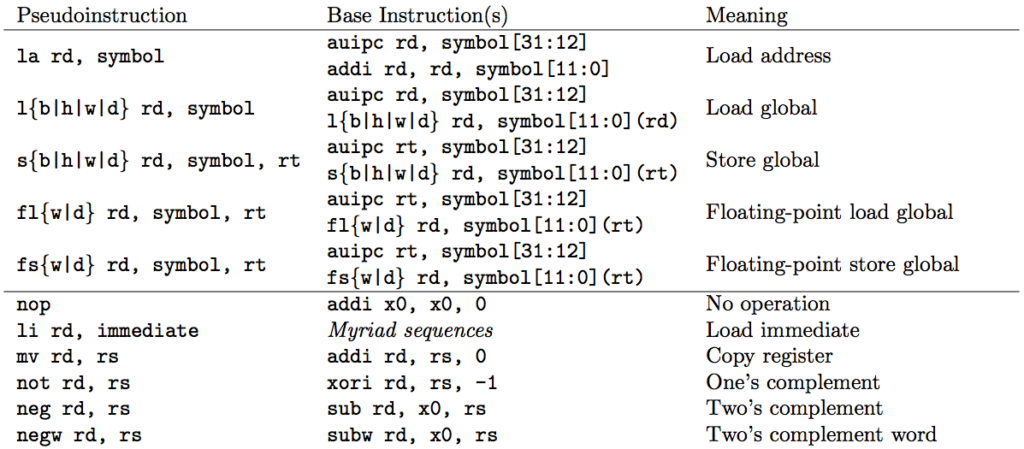

O assembler usa o registrador x0 como um espaço reservado para fazer manuseio de algumas operações, por exemplo o move rx to ry seria

- Soma rx com 0: add r0 to rx;

- Salva o resultado em ry: store in ry.

Registradores de controle e status também, mas somente o nível de privilégio mais alto (user) que poderá acessá-los para medição de performance.

Como todos os outros design de RISCs, RISC-V é um máquina load-store. Somente estas duas instruções que acessam a memória principal e todas as operações lógico-aritméticas ocorrem entre registradores.

Diferentemente de outros projetos RISC acadêmicos otimizados para simplicidade, o conjunto de instruções do RISC-V é desenvolvido para a praticidade de implementações, com características que aumentam a velocidade computacional enquanto reduz seu curso e energia.

Várias otimizações foram feitas como: 1) Colocar os bits mais significantes numa posição fixa; 2) Disposição de bits para reduzir o número de multiplexadores no CPU;

Eficiência

Foi projetado para alcançar altos e baixos níveis de velocidade com pouco gasto de energia e eletrônicos. Todas suas instruções possuem 32 bits e isso gera simplicidade, mas códigos com mais instruções.

RISC-V, intencionalmente, não possui códigos condicionais, nem mesmo bit de carry e sendo assim, os projetistas afirmam que isso pode simplificar o desenvolvimento do CPU, minimizando interações entre instruções. Construíram operandos de comparação dentro dos jumps condicionais, não possui carry de operações aritméticas complicadas nem tem detector ou flag para erros aritméticos, incluindo overflow, underflow e divisão por 0 (zero).

Foi desenvolvido para suportar sistema de memória e instruções inteira e ponto flutuante de 32, 64 e 128 bits. Suas funções load e store pode realizar operações com 16 e 8 bits, mas não operações aritméticas. Já as instruções de 64 bits, incluem aritméticas de 32-bits.

De Projeto Acadêmico À Item Comercial

O RISC-V Como Projeto Acadêmico

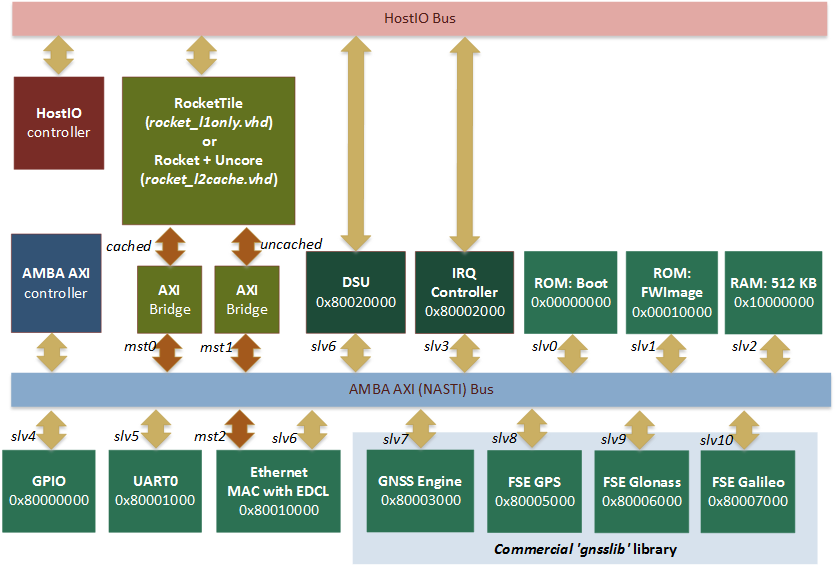

Projeto iniciado em 2010, foi disponibilizado em 2015 e já é utilizado em indústrias de grande porte como Google, Mellanox e Oracle além de grandes centros acadêmicos. Com isso vários projetos funcionais online já estão disponíveis, usufruindo da permissão de licença BSD. Um exemplo é o escalar de 5 estágios chamado RISC-V Rocket (Disponível em: https://github.com/ucb-bar/rocket) em Scala e para sintetização em chips (Disponível em: https://github.com/ucb-bar/rocket-chip).

ISA Modular

Instruções

O modelo de programação RV32I é escasso. Nele é contido Program Counter e 32 registradores inteiros (x0 – x31). Não contém registrador de retorno sendo este o x1.

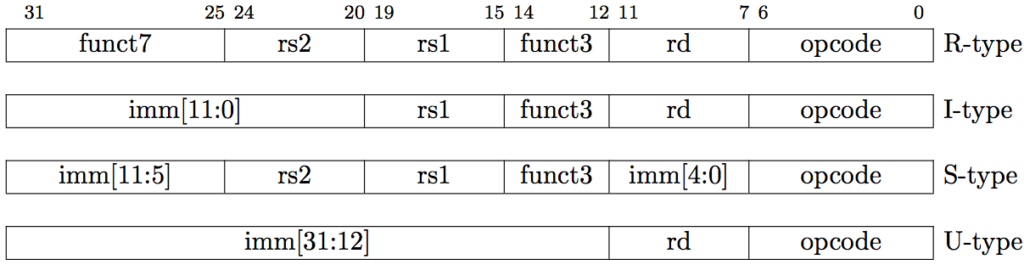

As instruções possuem 32 bits possuindo várias combinações de imediatos, operandos e outra especificações. O opcode e operando ficam em locais fixos, facilitando o processo de decodificação.

Modelo De Memória

Sua memória é endereçada por byte e utiliza-se little-endian.

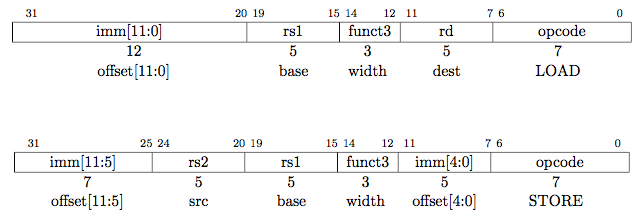

Enquanto outros processadores utilizam complexos instruções e modos de endereçamento, RISC-V usa somente base+offset.

Podem operar em dados de tamanho 8 (byte), 16 (half-word) ou 32 (word) bits além das opções de sinalização.

Variantes E Extensões

Variantes: RV32I, RV32E, RV64I E RV128I

Todas as outras variantes do RISC-V são baseadas do RV32I.

RV32E:

- Possui a meta para ser satisfatório para implementações de pequeno porte.

Sendo um projeto menor, ocupa-se uma pequena porção de área die. - Aumenta o custo/benefício de produção de chips;

Melhora a dissipação de calor por se tratar de um chip com menos área de circuito;

Isso reduz registradores para somente o Program Counter e x0-x15. - De resto, RV32E e RV32I são idênticos, com exceção de:

- Suas instruções continuam com tamanho de 32 bits. Os bits de maior índices são 0 (zero).

RV64I e RV128I:

- Simples extensões de 64 e 128 bits.

- Aumentam o espaço de endereço e estende os registradores de 32 para o tamanho apropriado.

- Essa extensão introduz novas instruções que operam com dados menores como 32 e 64 bits.

Extensão: Multiplicação

Multiplicação M:

- Adiciona 4 instruções de multiplicação, duas de divisão, e duas de manipulação de restos.

- A base é indicada pela base do ISA.

- A divisão por 0, por exemplo, não causa interrupção, mantendo a simplicidade.

Extensão: Sincronização

Sincronização A:

Adiciona 11 instruções de sincronização visando consistência e atomicidade da operação. São divididos em dois grupos: Load Reserved e Store Conditional para operações atômicas na memória.

Extensão: Ponto Flutuante

Possui três extensões diferentes: Precisão simples (F), Precisão Dupla (D) e quádrupla precisão (Q). A extensão F é pré-requisito para D, que é pré-requisito para Q.

Introduz também 32 registradores de ponto flutuante (f0-f31) de tamanho 32 bits e um registrador de 5 bits para exceções. Exceções não geram interrupções e com isso devem ser verificadas por meio de consultas.

As instruções load–store usam o mesmo endereçamento base+offset.

Extensão: Compressão De Tamanho De Código

A última extensão C não adiciona nenhum outra função, mas, ao invés disso, codifica as instruções inteiras para salvar espaço e com isso reduzir o tamanho do footprint. É disponível para bases inteiras, bem como load e store para pontos flutuantes e cria-se então instruções comprimidas em 16 bit. Basicamente, cada função compactada é mapeada diretamente à instrução real e possui algumas restrições para a compressão sobre o formato dos operandos.

O propósito de reduzir o tamanho do código binário, energia e custo para pequenos computadores, é visando sistemas embarcados. Pesquisas com C mostram que um código 20\% menor que um x86 e MIPS Comprimido e 2% maior que um ARM Thumb-2.

Níveis De Privilégios

Níveis De Privilégios

Existe 4 níveis de privilégios:

User (U);

Supervisor (S);

Hypervisor (H); e

Machine (M).

Para reduzir o custo de uma implementação de pequeno porte, somente o machine é obrigatório. Entretanto, todos os 4 privilégios são suportados e quando suportados, é possível até executar o Linux.

O Ecossistema Open-Source

O projeto ainda está em desenvolvimento, mas as especificações já mostram que é bastante promissor. Sua arquitetura é mais fácil de ser implementada do que um ARM, por exemplo pela sua simplicidade em decodificar códigos; e nos modos de endereçamento, omite instruções complexas e tudo isso com metade do tamanho de projeto de um ARM core.

É considerado como a técnica mais promissora em flexibilidade de extensões customizadas combinado com arquitetura de propósito geral.

Extensões potenciais do RISC-V incluem novos tipos como:

- Extensões Cray-style vector;

- Memória Transacional; e

- Manipulação de bit.

Outras extensões são disponibilizadas para obter melhor desempenho, mas requerem cadeias de ferramentas e limitam a portabilidade de software.

O ecossistema RISC-V ainda está nos estágios iniciais. Um Linux 4.1 foi sido portado para o projeto RISC-V e um Linux Embarcado (Yocto) também foi disponibilizado.

Várias ferramentas do RISC-V incluem compiladores GCC, LLVM e Clang, GDB, uma suite de verificação e simuladores.

Oferece todos os recursos básicos de um RISC com implementações simplificadas, reduzindo a die area e potencialmente, energia consumida por ele.

Comparado os dois modelos mais populares (ARM e x86)

- Oferece uma considerável área de circuito não utilizada em placa deixando o projeto menos custoso;

- Permite a adição de extensões customizadas ou não.

- É um projeto open-source.

Adoções Do RISC-V No Mercado

Um número de organizações comerciais planejam suportar o RISC-V Foundation, são algumas:

- Bluespec, Inc., Google, Hewlett Packard Enterprise (HPE), Lattice Semiconductor, Mellanox Technologies, Microsemi, Oracle e Rambus Cryptography Research.

- O Instituto Indiano de Tecnologia Madras estão desenvolvendo 6 RISC-V open-source para 6 tipos de usuários diferentes.

- De um pequeno CPU 32 bit para IoT até largos computadores de 64 bit concebido para computadores em escala de de armazenamento.

- lowRISC é um projeto sem fins lucrativos que visa implementar um sistema open-source num System on Chip (SoC) baseado num RISC-V de 64 bits.

- O Laboratório de Computação, na Universidade de Cambridge, em colaboração com o FreeBSD Project, tem suportado o sistema operacional FreeBSD para o RISC-V 64-bit.

- ETH Zurich e a Universidade de Bologna têm desenvolvido em cooperação um System on Chip (SoC) de baixa energia usando RISC-V.

- Um dos fundadores do Adapteva planeja usar RISC-V como sucessor para o seu produto acelerador multicore.

- Nvidia planeja usá-lo para substituir a linha de processadores Falcon em suas placas gráficas GeForce.

Article Name: RISC-V

Description: Introdução ao RISC-V

Author: Rodolfo Labiapari Mansur

Publisher Name: Laboratório iMobilis

Referência: http://www2.decom.ufop.br/imobilis/o-risc-v/