Breve Introdução Sobre Open-Source FPGA

Sabemos que um FPGA geralmente é utilizado para vários propósitos. São alguns deles:

- Processamento Digital de Sinais (DSP);

- Processamento Paralelo de Dados;

- Interface de Hardwares customizados;

- Protótipos de projetos ASIC; e muitos outros.

Alguns fabricante deste tipo de circuito são Xilinx, Altera, Lattice, Microsemi, etc. É importante ressaltar isso pois mesmo que a linguagem HDL seja a mesma, o processo de geração de síntese difere em cada uma delas pois cada uma tem sua característica de fabricação. Isso também leva a cada fabricante possuir seu próprio conjunto de ferramentas para sintetização. São algumas:

- Altera Quartus;

- Xilinx Vivado/ISE;

- Lattice Diamond; etc.

Obviamente, essas respectivas ferramentas possuem código fechado e todas seguem a mesma ideia de funcionamento onde passam pelo processo de:

- Análise e Síntese: possui como input HDL transformando-o em uma Netlist;

- Pack, Place e Route: usam a Netlist para gerar uma Netlist de Tecnologia Mapeada; e por fim

- Assembler: gera-se o bitstream usando a Netlist de Tecnologia Mapeada sendo este, o projeto final para ser transportado à placa.

Também é com que estas ferramentas realizem Análise de Tempo sendo esta importantíssima para projetos de alta velocidade verificando restrições de tempo e também Simulação e Visualização para validação.

Introdução Ao Bitstream

Sabendo de antemão o conceito de FPGA, vamos mais a fundo explicando um nível mais baixo presente na sintetização de um projeto. Assim, nesta introdução falaremos sobre bitstream, termo não comumente conhecido para os novatos na área.

O bitstream, que significa fluxo de bits é uma série temporal de bits.

Este padrão é utilizado extensivamente não só em computação como também em telecomunicações como por exemplo:

- A tecnologia de comunicação SDH transporta fluxos de bits síncronos; e o

- Protocolo de comunicação TCP transporta um fluxo de bytes sem temporização síncrona.

Já no âmbito real de FPGA dentro de computação, o termo bitstream possui origem diferente do seu uso de fato. O termo pode ter se originado num método comum de configuração do FPGA de um fluxo de bits serial o que normalmente seria em um chip serial PROM ou memória flash. Entretanto, apesar desta tecnologia, muitos FPGA também suportam método de carregamento de bytes paralelo.

Seu formato é utilizado para descrever os dados de configuração a serem carregados no FPGA, assim, o formato detalhado do fluxo de dados para um chip FPGA particular é geralmente considerado proprietário do vendedor do FPGA.

É comum encontrar aquivos de bitstream criptografados. Isso acontece pelo fato de seus projetistas tornarem seu projeto uma propriedade intelectual, ato não abraçado pela comunidade open-souce.

A seguir serão descritos algumas informações sobre ferramentas open-souce para a geração, validação e simulação de projetos bem como uma análise final sobre o estado da arte.

Passos De Compilação

Análise E Síntese

Análise pode-se dizer que é a verificação do HDL por completo. Ocorre a validação da corretude de escrita tal como é feito com os processos front-end de um compilador comumente conhecido (léxico, sintático e semântico).

Já a Síntese é o processo que gera uma Netlist a partir do HDL fornecido como entrada.

A junção destas duas ferramentas tem-se que modelos comportamentais resultam em esquemáticos de circuitos.

Algumas ferramentas open-source para esta etapa são:

- Icarus Verilog;

- Odin II; e

- Yosys.

Icarus Verilog

Realiza simulação, tradução e síntese de HDL e a ferramenta possui licença GPL com exceção de seus plugins. Possui como entrada Verilog 2005, System Verilog e VHDL com suporte mais limitado e como saída, é possível gerar um Verilog minimizado/simplificado, tradução para VHDL e Netlist para Gate-Level.

Está disponível em: http://iverilog.icarus.com/

Odin II

Framework de síntese com suporte a visualização. Possui licença MIT. Sua entrada é um código Verilog ou Netlist BLIF e como saída, obtêm-se a síntese.

Disponível em: https://code.google.com/archive/p/odin-ii/ e Git disponível em: https://github.com/verilog-to-routing/vtr-verilog-to-routing/tree/master/ODIN_II

Yosys

Suite de síntese HDL com licença ISC. Possui as mesmas entradas do Odin II e como saída possui vários formatos de Netlist e também um Verilog simplificado.

Este software está disponível em: http://www.clifford.at/yosys/

Place E Route

Consiste em várias sub-etapas, sendo elas a Pack, Place e Route. Pack gera vários blocos largos por meio da Netlist, Place define onde os blocos vão ser alocados no FPGA e o Route realiza a interconexão entre cada bloco.

Algumas ferramentas:

- Arachne PnR; e

- VPR.

Arachne PnR

Trabalha especificamente com o iCE40 FPGA da Lattice e sua entrada é a a saída do Yosys. Como saída possui a representação textual do bitstream.

Disponível para download em: https://github.com/cseed/arachne-pnr

VPR

Sigla de Versatile Placement and Routing é uma ferramenta extremamente flexível podendo trabalhar com qualquer tecnologia FPGA. É bastante utilizado em pesquisas em FPGA e também em âmbito comercial.

Disponível em: http://www.eecg.toronto.edu/~vaughn/vpr/vpr.html

Assembler Tools

Transforma a Netlist já montada em formato bitstream, lembrando que este é o último estágio da ferramenta para configuração de um FPGA.

A uma ferramenta disponível chama-se IcePack e está disponível em: http://www.clifford.at/icestorm/. Ela é um assembler para iCE40 FPGA da Lattice e faz parte do projeto maior chamado IceStorm.

De forma geral o IcePack pega a representação textual do bitstream e a transforma em bitstream binário.

Aforementioned

Fazendo um resumo de tudo que foi passado, é possível desenvolver uma ferramenta com fluxos completos, ou seja, é possível pegar um HDL e produzir o bitstream dele. Um exemplo desse é o IceStorm.

IceStorm

É possível gerar um fluxo bitstream completo a partir do Verilog. Ele é específico para iCE40 e utiliza as ferramentas Yosys, Arachne PnR e IcePack consecutivamente.

Além disso eles possui ferramentas adicionais próprias como IceProg para programação no FPGA e também o IceTime para análise de tempo. É tido como uma das ferramentas mais completas (open-source) existentes atualmente e também está disponível em: http://www.clifford.at/icestorm/

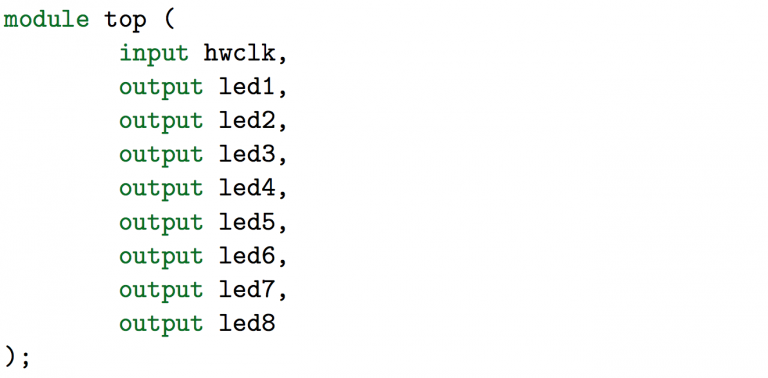

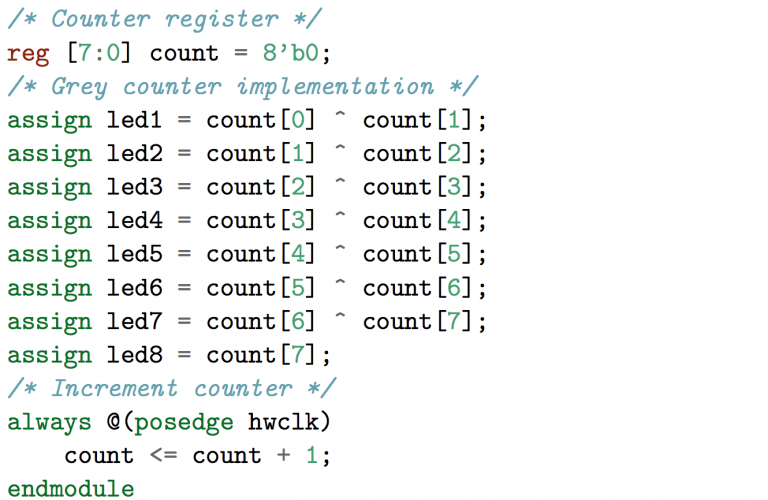

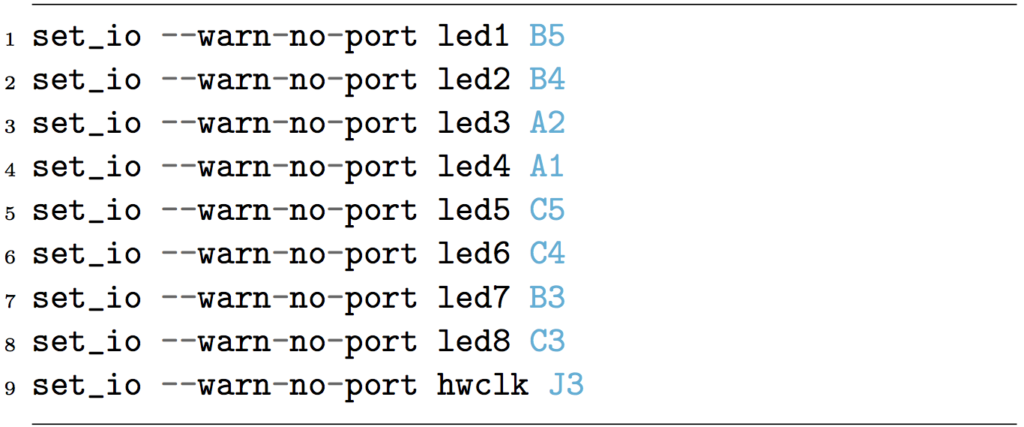

Exemplo De Utilização Do IceStorm Para Um Gray Counter

Simulação E Visualização

Ferramentas open-source fpga:

- gHDL

- Verilator

- Icarus Verilog

GHDL

É uma ferramenta de simulação de VHDL onde ela compila o VHDL para seu código nativo. Utiliza-se backend de construtores internos além de GCC e LLVM para a geração do código.

Seu simulador é de fácil interpretação e possui como saída VCD (Value Change Dump, Verilog orientado) e gHDL waveform.

Esta ferramenta está disponível em: http://ghdl.free.fr/

Verilator

Realiza-se a síntese do Verilog para C++ além de análises de otimizações durante a sua síntese. Suporta entradas Verilog, Verilog 2005, System Verilog.

Ela está disponível em: http://www.veripool.org/wiki/verilator

Icarus Verilog

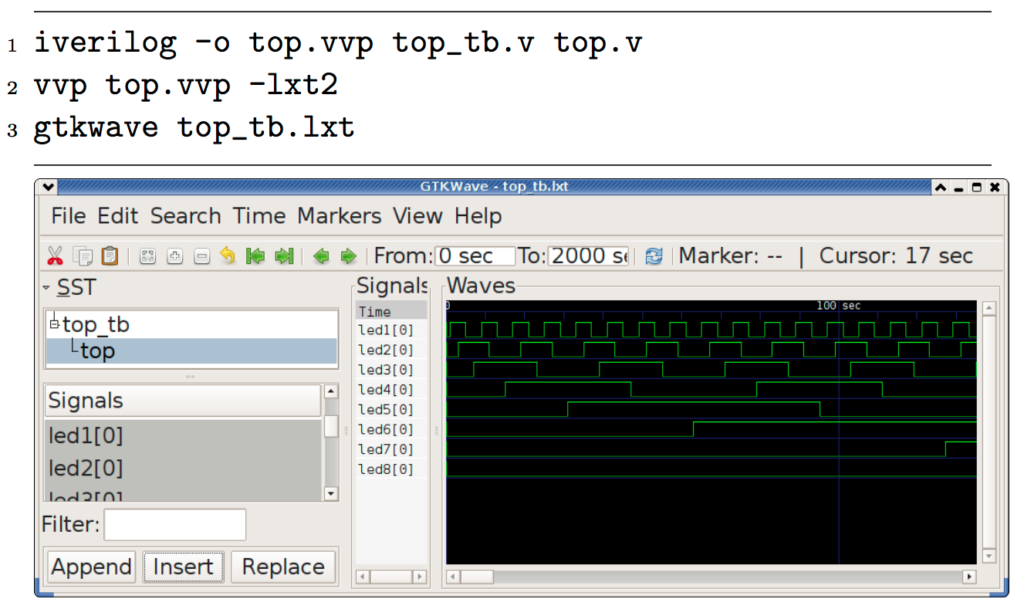

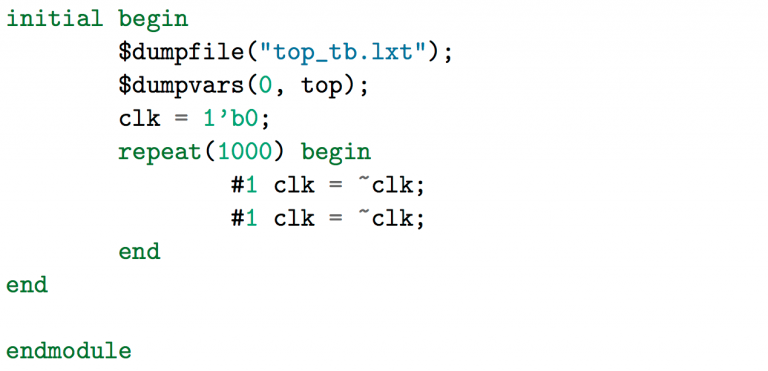

Primeiramente essa ferramenta tida como um simulador e tradutor, disponível em http://iverilog.icarus.com/ . Ela realiza a compilação do HDL e para um código intermediário chamado VVP e é extremamente útil para escrita de testbenches. Produz como saída GTKWave.

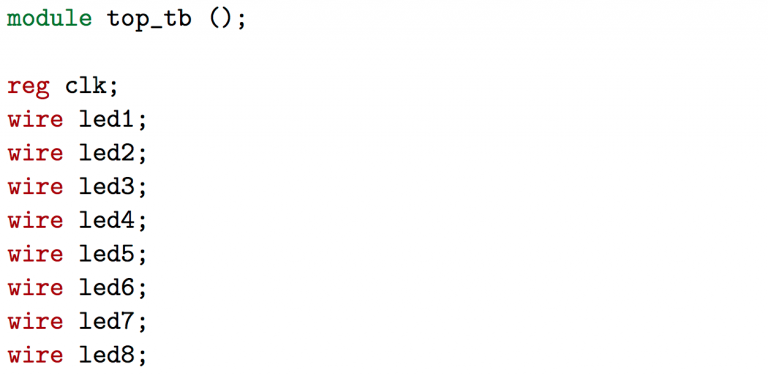

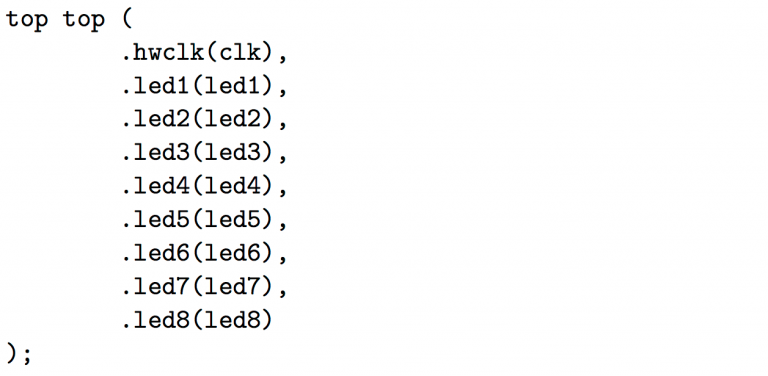

Exemplo

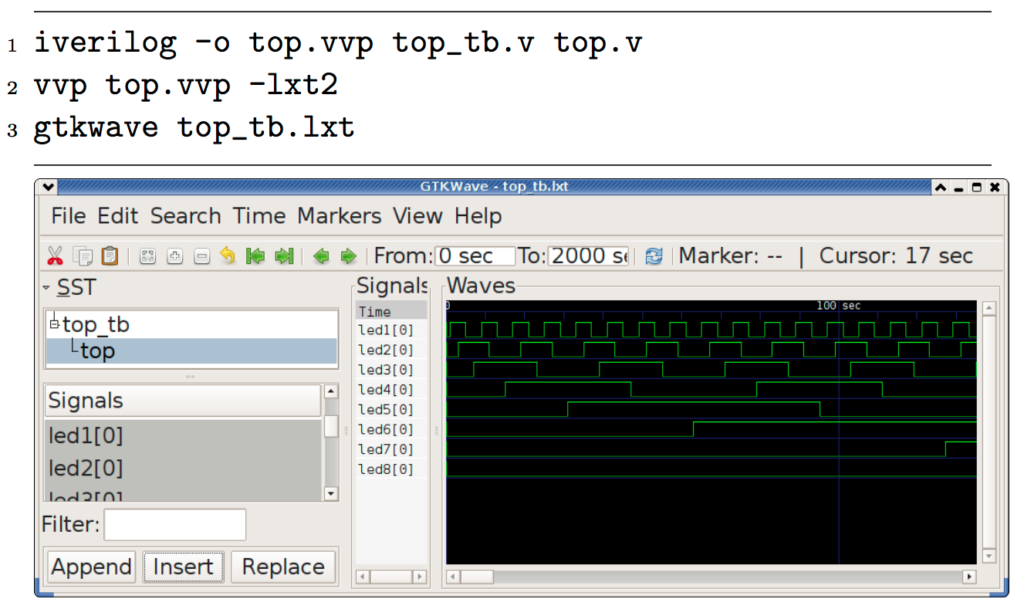

Visualização Utilizando O GTKWave

Como já mencionado, GTKWave é uma ferramenta de visualização de ondas em simulação e está disponível em http://gtkwave.sourceforge.net/. Suporta inúmeros formatos como VCD, LXT, FST e outros.

Trabalha excelentemente bem com outras ferramentas como gHDL, Icarus Verilog, etc.

Mas Por Por Que Tais Ferramentas São De Complexidade Mais Elevada?

Primeiramente pela falta ausência de documentações para seu uso. Outro item bastante importante é o receio do desapego de algoritmos com pessoais para a comunidade livre e também o retrocesso por parte dos fabricantes e suas propriedades intelectuais.

O DeBit

O DeBit é uma tentativa de documentação dos FPGAs da Altera e Xilinx. O projeto aparece inativo e sua documentação textual ainda possui muitas lacunas. Possui grande quantidade de código C encriptado e suporta somente FPGAs de modelo antigo. É uma ferramenta que permite fazer dumping de um bitstream de uma parte específica fazendo a engenharia reversa desta.

Summary

Article Name: Ferramentas Open-Source para Design de projetos em FPGA

Description: How many tools do you know that use open-source for a FPGA Design?

Author: Rodolfo Labiapari Mansur

Publisher Name: Laboratório iMobilis