Introdução Ao Risc-V IoT

Risc-V IoT:IoT são dispositivos de função única que são conectados à internet. Tais dispositivos como lâmpadas, geladeiras, janelas, portões passam por três procedimentos principais:

- Sensoriamento: Acelerômetro, giroscópio, pressão, temperatura…;

- Processamento: Encriptação, processamento digital de imagem, filtro de dados…;

- Comunicação: Wi-Fi, Bluetooth, I2C, SPI, Zigbee…

Platafoma Risc-V IoT No FPGA Sobre Tecnologia Da Lattice

Segundo a empresa de fabricação de semicondutores, uma plataforma de Risc-V IoT em FPGA deve ser de fácil utilização usando linguagens como C/C++ para desenvolvimento para clientes finais além de usuários poderem escrever aceleradores em hardware usando C e não HDL. No projeto apresentado por eles, utilizam o RISC-V com aceleradores LegUp, desenvolvidos por eles. Outro item importante que deve compor ao projeto é a flexibilidade. Deve suportar uma gama de sensores, atuadores e API de dispositivos comunicadores. Além disso, deve possui capacidade de gerar instruções customizadas ou bibliotecas de aceleração caso necessitada em projeto desenvolvido pelo usuário. FPGA é a arquitetura que preenche perfeitamente esse requerimento.

Combinando o processador RISC-V com o hardware FPGA, obtêm uma solução híbrida com baixo consumo de energia e pequeno footprint, ponto chave para toda plataforma IoT.

Fazendo uma associação do sistema IoT descrito anteriormente à solução reconfigurável, temos:

- Sensoriamento: Descrição em software de componentes sensoriais. A plataforma Lattice IoT fornece várias API para vários sensores e atuadoros;

- Processamento: Processador RISC-V juntamente com o acelerador sintetizado em hardware reconfigurável juntamente. Realizar o casamento do RISC-V com o hardware acelerador gerado LegUp para o manuseio de de parte de um processamento de uma plataforma IoT, tem-se um:

- Baixo consumo de energia e pequeno footprint gerado;

- Após identificar pontos críticos em programas em C, usar o LegUp para sintetizá-los num FPGA e aumentar a performance do sistema;

- As partes não críticas do programa em C são executadas pelo processador RISC-V;

- Tudo isso mantendo o baixo consumo de energia e a alta vazão.

- Comunicação: Descrição em software para dispositivos comunicáveis. Item também suportado pela plataforma para IoT Lattice.

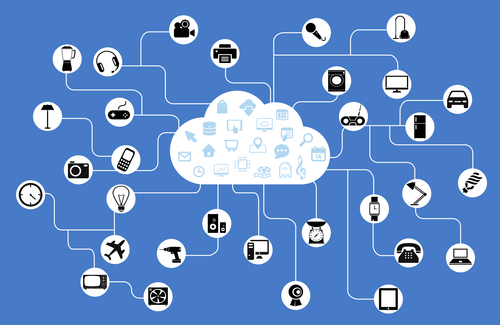

Arquitetura RISC-V Com Aceleradores LegUp

Abaixo é exibido um diagrama mostrando como seria um sistema que utilizasse o processador RISC-V em conjunto com o acelerador LegUp.

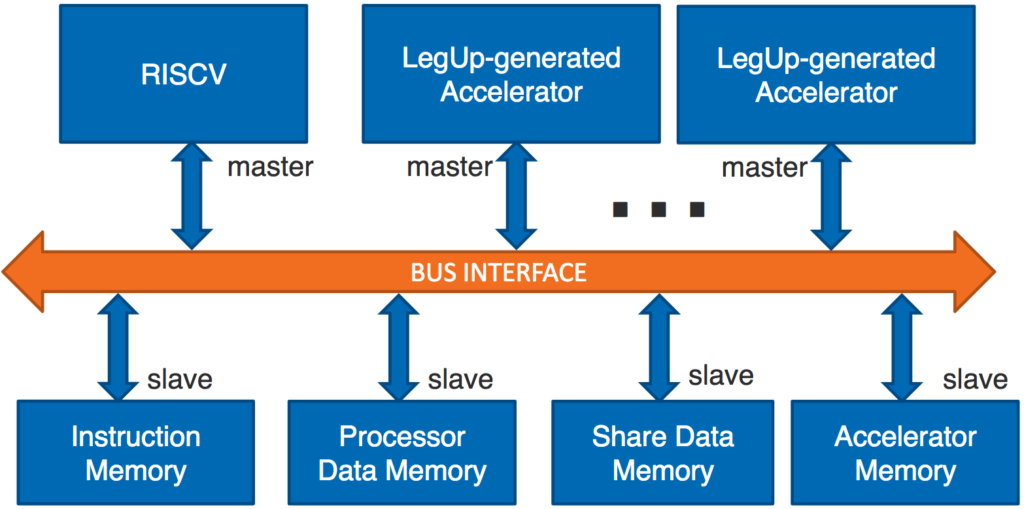

O processor Lattice RISC-V possui o seguintes passos de pipeline.

Como é possível ver, ele possui 4 estágios e se baseia no ISA RV32IMC que inclui os subconjuntos RV32I, RV32M para multiplicadores e RV32C. Outras características adicionais podem ser configuradas por meio de parâmetros em Verilog.

Síntese De Alto-Nível Em LegUp

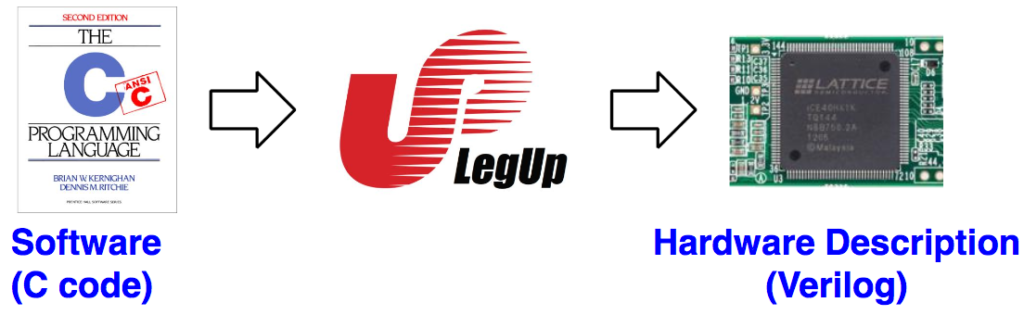

Abaixo é exibido uma demonstração de como é realizado o processo de geração de código HDL a partir de um código C.

Vantagens Do Uso Do LegUp

O primeiro e principal é que muitos desenvolvedores não conhecem a linguagem Verilog ou muito menos qualquer HDL. Projetos que levariam meses agora leva semanas.

Argumentam também que testbench realizados sobre a linguagem C são até cem vezes mais rápido que simulações feitas em linguagem HDL. Permite a exploração de espaços de design além da fácil ‘debugação’ da linguagem C.

LegUp Design Flow

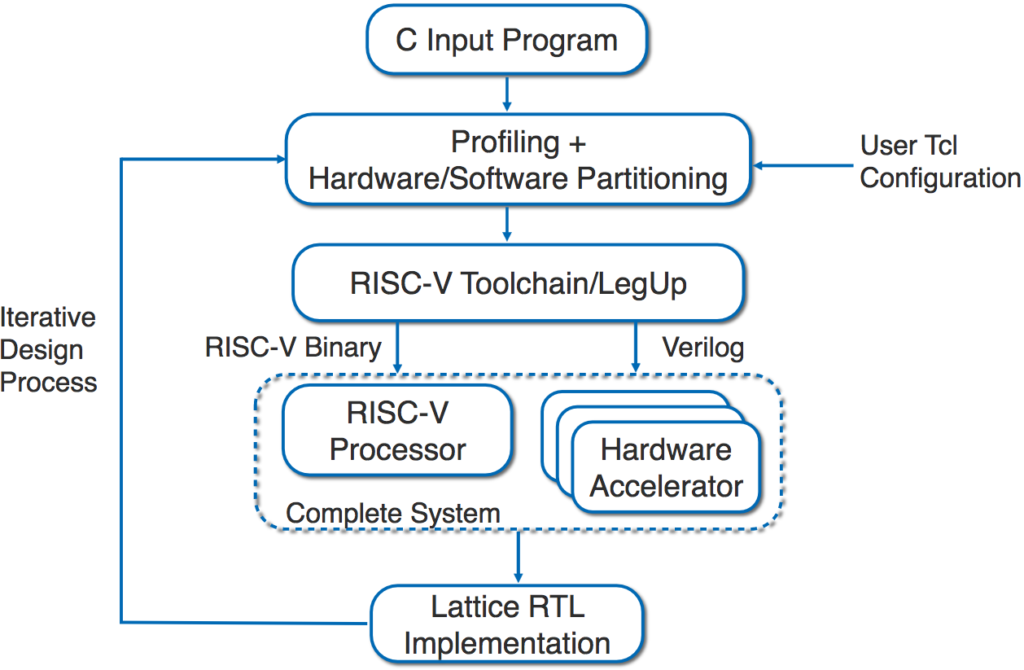

O procedimento de geração de código a partir do LegUp é realizado a partir do seguinte fluxograma.

Inicialmente é escrito o código em linguagem C e adicionado todas as informações de compilação. O processo irá gerar o Processador RISC-V, pedaços especificados de programas gerado em HDL e o resto dos programas binários gerados ambos a partir da linguagem C. O que isso significa? Significa que pedaços do programa que pode ser executado em nível de hardware podem ser gerados HDLs específicos para tais e consequentemente criando módulos únicos para cada. Com isso, tem-se o processador descrito em HDL, o código executado por ele em C e pequenos módulos em HDL localizados no mesmo ambiente onde se encontra o RISC-V chamado de aceleradores (tão falado nos últimos posts de RISC-V :>).

Gerado o sistema por completo, obtêm-se o projeto em RTL.

Exemplo De Criação De Um Acelerador

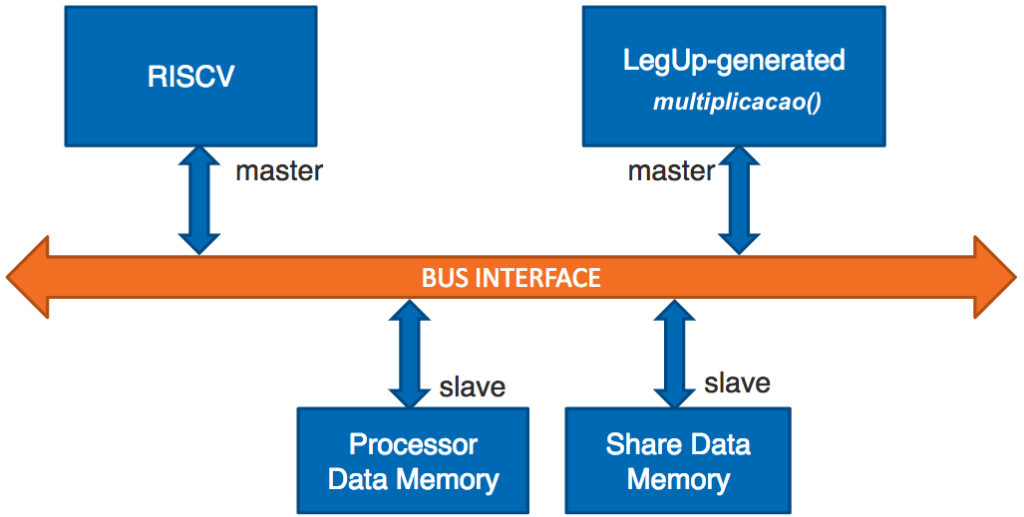

Supondo que tem-se uma função num código em C chamada multiplicacao. Para acelerar esta função em nível de hardware basta especificar no LegUp Tcl o comando set_accelerator_function ”multiplicacao” e executar o LegUp.

Internamente, o LegUp irá transformar o código adaptando-o para o acelerador Verilog de hardware. Automaticamente ele irá modificar a função criando um wrapper para a interface de hardware e modificando também a chamada da função que receberá um novo nome sendo este legup_multiplicacao. Ao fim, terá um acelerador dedicado à função especificada.

Ao final, o projeto estará da seguinte forma.

Caso De Estudo

Supõe-se que temos o seguinte código:

[code language=”c”]

for (i = 0; i < 256; i++)

energia += amostras[i] * amostras[i];

[/code]

A energia de determinado item é calculado pelo quadrado de uma amostra. Sabendo do código citado, analisemos.

Processamento No RISC-V32IM

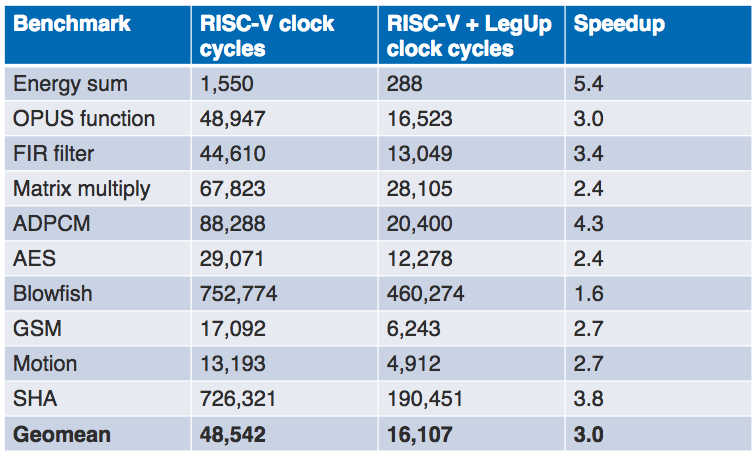

É possível perceber que cada loop toma pelo menos 6 ciclos sendo eles load, increment, address, multiply, add e branch. Este processamento leva cerca de 1550 clocks para ser completado.

Processamento Com O Acelerador Sintetizado Pelo LegUp

Usando o mesmo código mas com olhos em sua sintetização em hardware, fica claro que será gerado um circuito em nível de hardware que explorará o paralelismo. Partindo deste, cada iteração será executado em um único ciclo de clock. Assim, o procedimento completo será executado em 288 ciclos de clock.

Com o novo valor de speedup temos uma melhora de 5,4 vezes da performance anterior.

Exemplos De Projetos Risc-V IoT

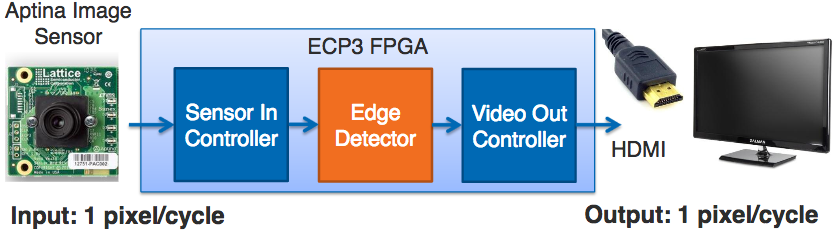

Na figura abaixo, é exibido um como seria o esquema de um projeto que utilizaria um módulo câmera, e saídas de vídeo além de processamento sobre os dados.

Os procedimentos para captura de imagem seriam descritos em linguagem HDL, o algoritmo para operação dos dados seriam escritos em linguagem de alto nível sendo executados em processador RISC-V IoT e o processamento para saída de vídeo também seria descrito em linguagem HDL.

Ao invés de utilizar todos processamentos, tanto de entrada e saída, em linguagem de alto nível, realizar a aceleração de alguns deles tornando módulos a parte ao processador pode tornar o projeto mais eficiente e reduzir o gasto de energia.

A tabela abaixo exibe o ganho do uso de LegUp ao transformar módulos em aceleradores em cada algoritmo.

Article Name

Plataforma Software-Programmable IoT FPGA pela Lattice

Description

Projeto que baseia no ISA RV32IMC que inclui os subconjuntos RV32I, RV32M para multiplicadores e RV32C e aceleradores.

Author – Rodolfo Labiapari Mansur

Publisher Name – Laboratório iMobilis