Introdução Ao Rocket Chip

O Gerador SoC Rocket Chip é um gerador parametrizado SoC escrito em linguagem Chisel.

Chisel é uma linguagem open-source de construção de hardware desenvolvida pela Universidade da Califórnia, Berkeley e está disponível em https://github.com/ucb-bar/chisel3/. Suporta design de hardwares avançados usando geradores altamente parametrizados e outros recursos. Algumas propriedades dela são:

- Hardware construction language (not C to Gates)

- Embedded in the Scala programming language

- Algebraic construction and wiring

- Abstract data types and interfaces

- Bulk connections

- Hierarchical + object oriented + functional construction

- Highly parameterizable using metaprogramming in Scala

- Supports layering of domain specific languages

- Sizeable standard library including floating-point units

- Multiple clock domains

- Generates low-level Verilog designed to pass on to standard ASIC or FPGA tools

- Open source on github with modified BSD license

- Complete set of docs

- Growing community of adopters

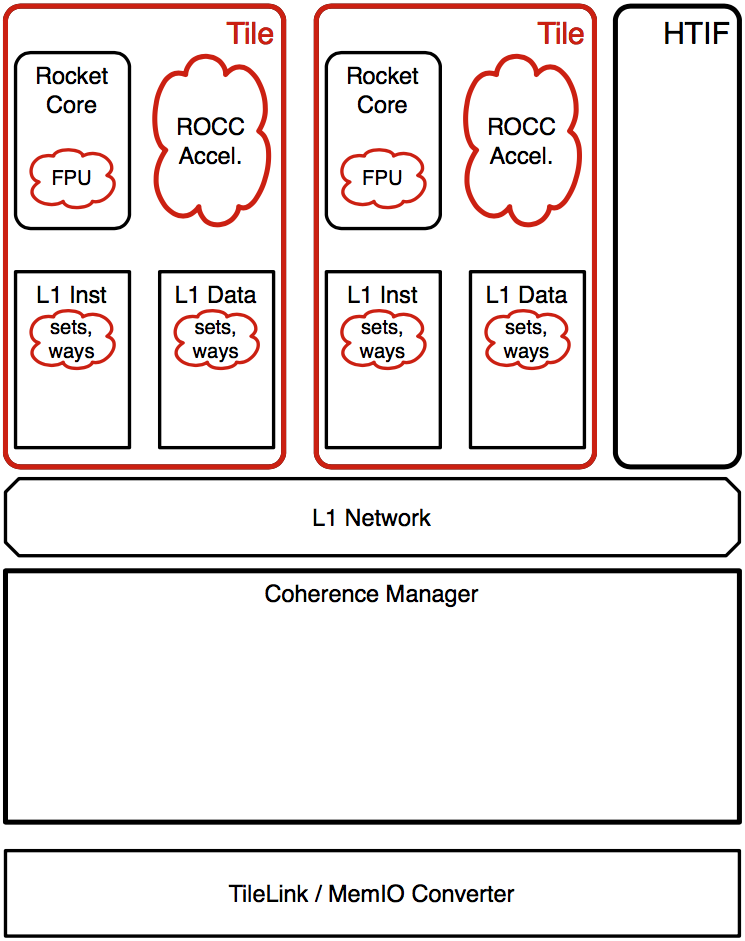

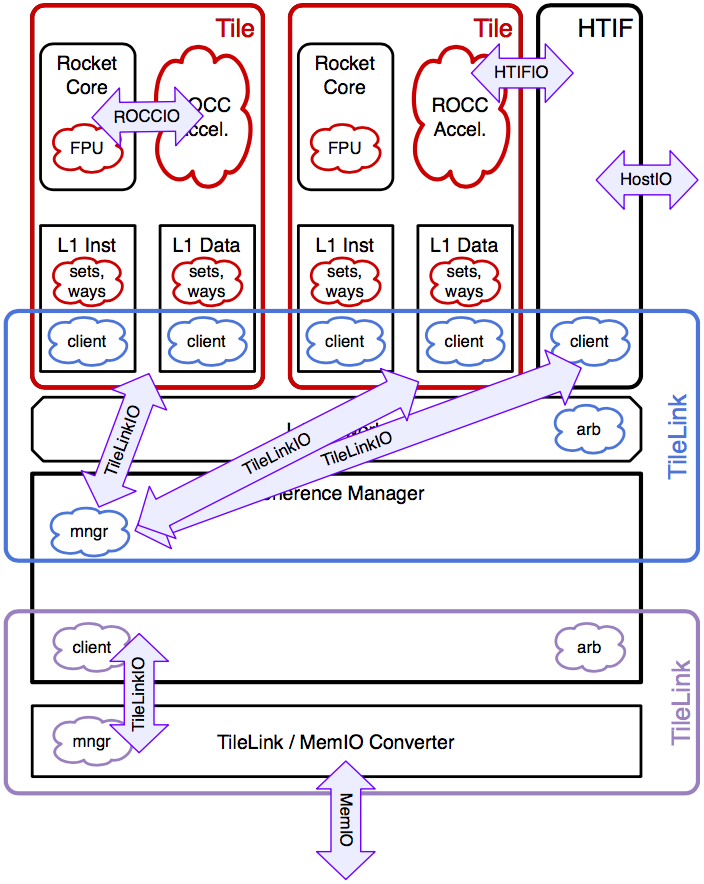

Com o Rocket Chip SoC Generator é possível gerar blocos como um core (Rocket) incluindo suas caches privadas além de itens que ficam na parte externa como caches compartilhadas, mecanismo de DMA e todo o controlador de memória necessário aglutinando todas estas peças numa única ao final do processo.

Cada tipo de bloco possui seus próprios componentes como é exibido abaixo.

Porque Utilizar Um Gerador SoC?

Um gerador pode ajudar a definir o design sobre diferentes formas de performance, energização, restrições de área utilizada e diversos outros itens tecnológicos a serem abordados numa construção de um sistema. É possível gerar diferentes arquiteturas para diferentes aplicações finais, incluindo a fácil alteração deste .

Possuem como parâmetro:

- Número de cores;

- Unidades de ponto-flutuante e vetoriais prontas e otimizadas;

- Alteração em tamanho de cache e outros da tecnologia;

- Alteração do número de estágios de diversos pipeline;

- Configurações de I/O do sistema.

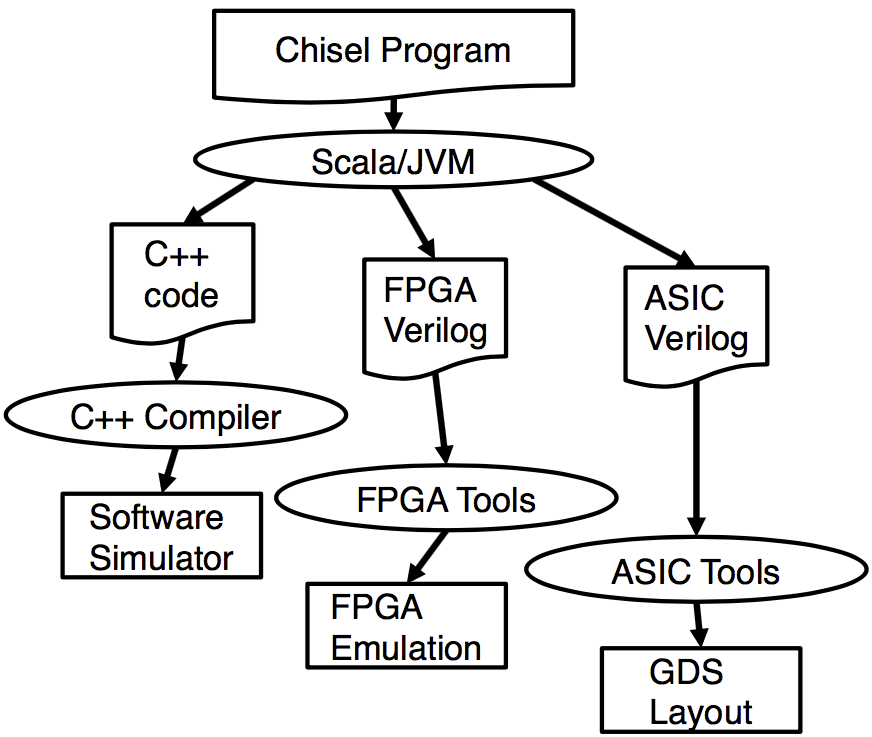

O fato de utilizar o Chisel vem a robustez fornecida pela linguagem base Scala. Ela fornece recursos suficientes para escrita de geradores utilizando programação orientada à objeto além de funcional o que permite gerar vários tipos saída para o design. O processo possui três pacotes principais e são exibidos no diagrama abaixo.

Características Gerais Do Rocket Chip

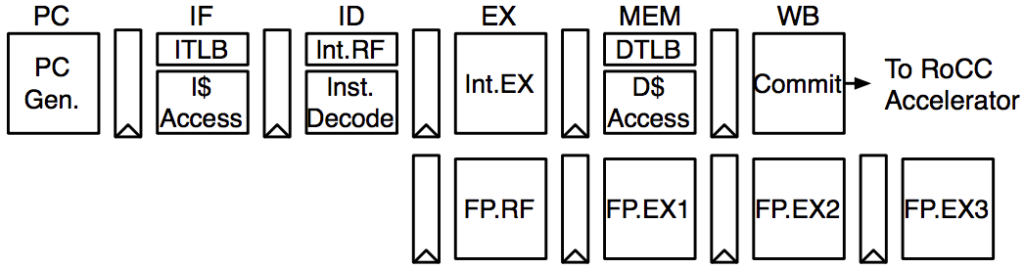

Core Escalar Rocket

- 64-bit com pipeline de 5 estágios em ordem;

- Design com intuito de minimizar impacto de delays de longo clock;

- MMU suporta memória virtual paginada;

- Unidade de ponto flutuante padronizado pelo IEEE 754-2008.

Comparando com um ARM Cortex-A5, o RISC-V Rocket possui até 49% menos de área mantendo a mesma eficiência.

Abaixo é exibido um exemplo do Pipeline deste.

HTIF: Host-Target Interface

É um bloco específico usado para emular dispositivos para testes simples com chips. É possível emular chamadas de sistemas, consoles, dispositivos de bloco (block devices), dispositivos de rede e outros. Este não é necessário quando se te dispositivos para teste. É tudo como o Mecanismo Hospedeiro de DMA.

Principais Interfaces Presentes No Rocket Chip

- RoCCIO: Interface de comunicação entre Rocket Core e o Acelerador;

- HTIFIO: Leitura e Escrita no CSR;

- TileLinkIO: Comunicação Interna entre blocos;

- MemIO: Interface simples de memória AXI-like;

- HostIO: Interface central para HTIF.

Abaixo serão descritos com maior detalhes.

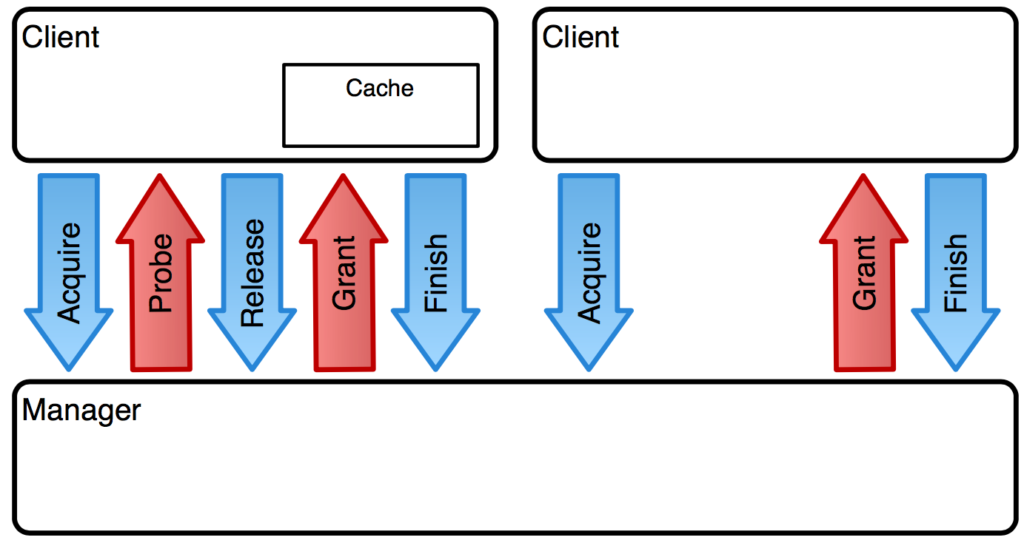

TileLinkIO

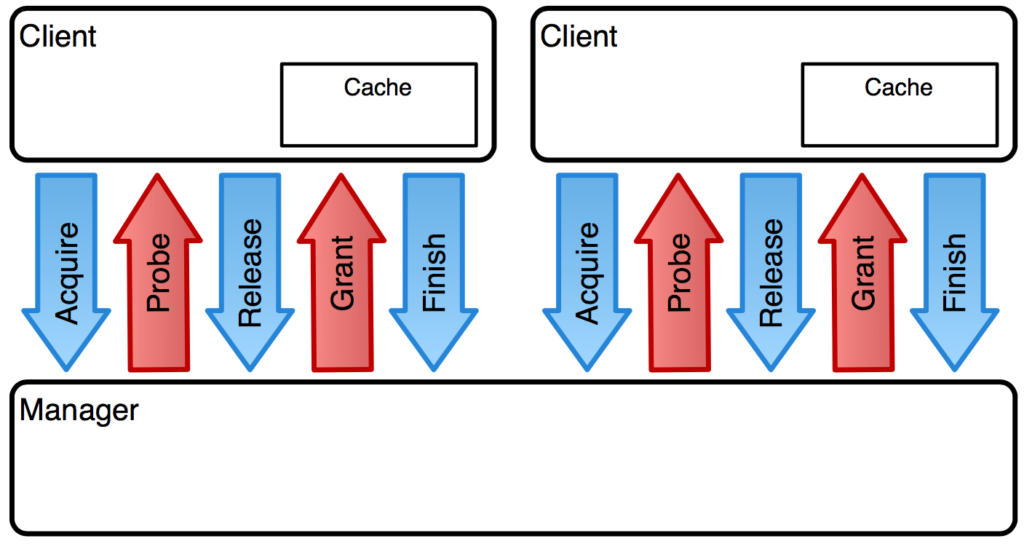

Fazendo uma ilustração, supõe-se que existe dois clientes, ambos com cache, comunicando com o gerenciador. Realiza a comunicação entre os blocos utilizando um protocolo nos quais consiste em Acquire, Probe, Release, Grant e Finish.

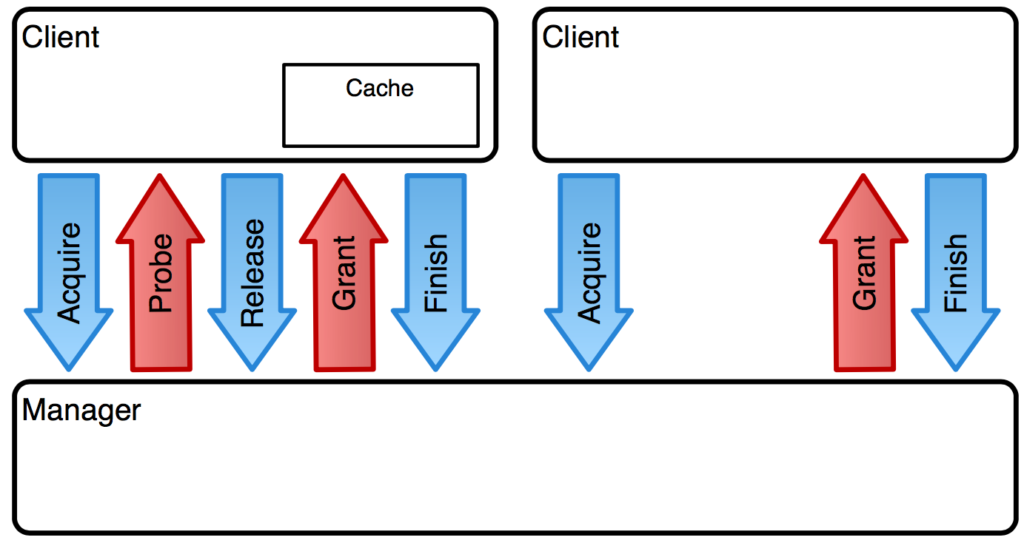

Além deste, também existe para comunicações onde não possuem cache como é exibido abaixo.

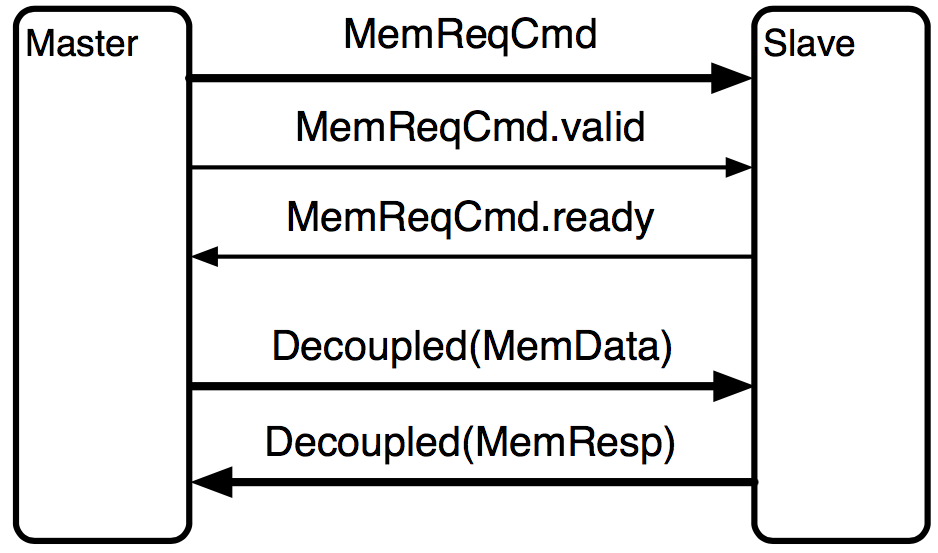

MemIO

Na interface de comunicação com a memória o Cmd representa no endereço e rw da ação requisitada. MemData e MemResp possuem barramento de 128 bit e o Decoupled(Interface) corresponde uma interface ready ou com sinais válidos.

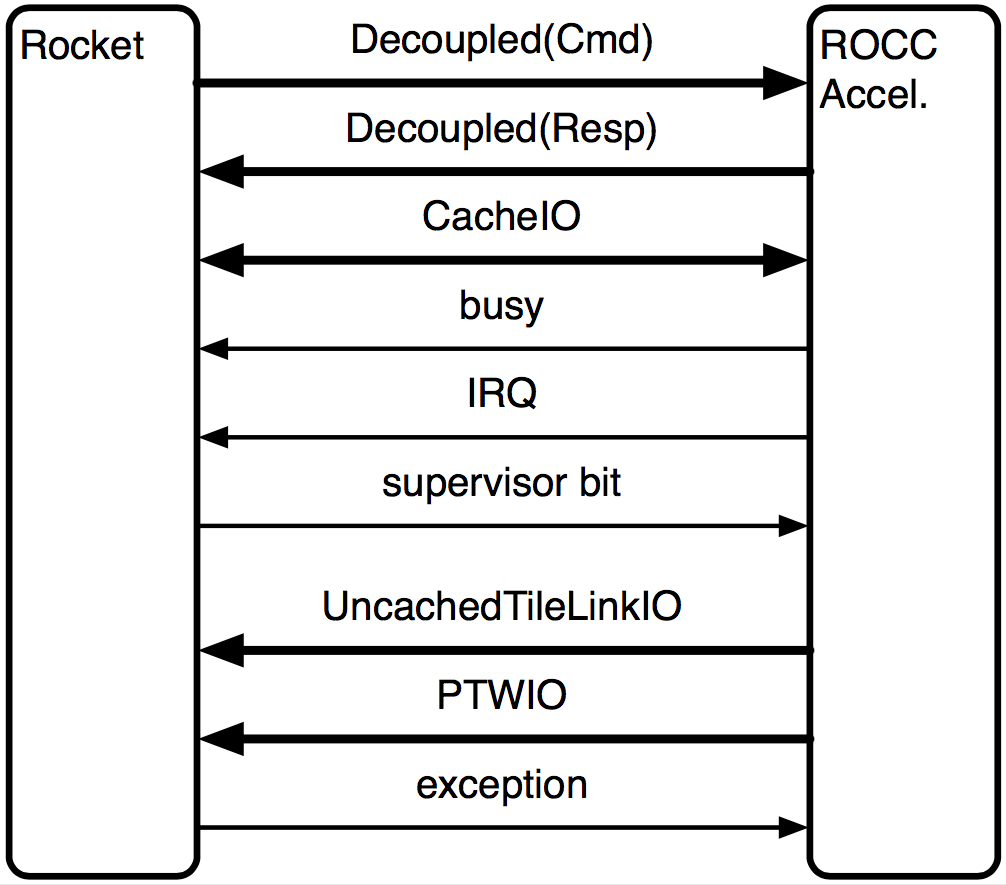

RoCCIO

Interface que realiza a comunicação de instruções do Core Rocket até o co-processador via interface Cmd onde responde pela via Resp, UncachedTitleLinkIO para o cache de instruções no RoCC.

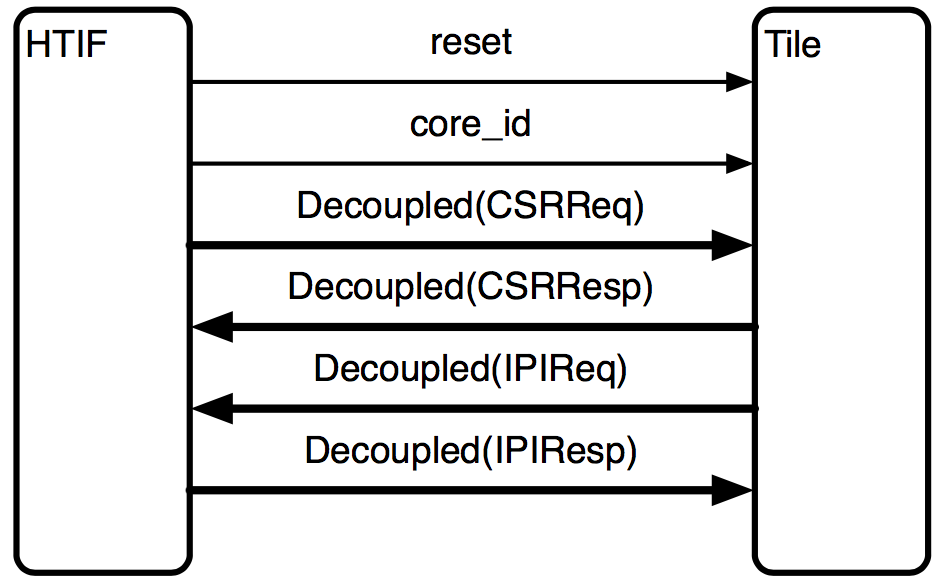

HTIFIO

HTIF tem como sigla host-target interface. Este é responsável pela comunicação com do Rocket com outros itens dentro do sistema.

Um exemplo em baixo nível pode ser verificado por meio da figura.

Setups

Nesta seção, será exibido como é o comportamento do Rocket Chip perante o mundo exterior e suas necessidades para a execução.

Pra Quem Se Destina O Gerador Rocket Chip?

Tal gerador é disponibilizado principalmente para todos os desenvolvedores de sistema embarcados. Pessoas que necessitam mais que só uma utilização do produto, ou seja, o desenvolvimento, a modificação deste.

Assim, para cada tipo de requisito, deve-se procurar seu respectivo parâmetro de configuração. Por exemplo, caso queria somente construir um RISC-V deve-se olhar para os parâmetros do Chisel. Para desenvolver um novo tipo de acelerador, deve-se estudar também o nível de configurações do RoCCIO.

Da mesma forma, construir um novo RISC-V Core, deve-se também estudar os níveis do TileLinkIO e MemIO para especificar o comportamento deste e por fim, adicionar um novo device é preciso ler sobre TileLinkIO ou UncachedTileLinkIO.

Article Name: Rocket Chip como SoC Generator in Chisel

Description: Com o Rocket Chip SoC Generator é possível gerar blocos como um core (Rocket).

Author: Rodolfo Labiapari Mansur

Publisher Name: Laboratório iMobilis

Referência: http://www2.decom.ufop.br/imobilis/rocket-chip-soc-generator-chisel/