Energia é tudo num SoC Risc-V

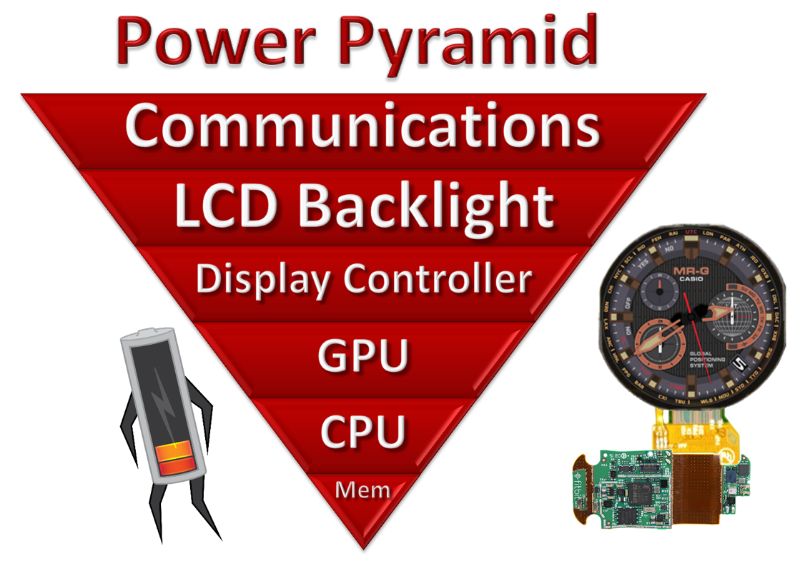

Vamos analisar a questão no SoC Risc-V. Para deixar mais claro o assunto tratado, olhemos o diagrama abaixo.

A pirâmide representa os itens que possuem maior consumo de energia dentro de um sistema embarcado. Será o item campeão em gasto de energia e em seguida será apresentado uma estratégia open-source para o tema.

A Comunicação Com O SoC Risc-V

De forma a salvar energia, sistemas de rádios em wearable ficam em modo inativo na maior parte do tempo e sendo ativados só quando necessário. Sendo assim, eles acordam, enviam ou recebem o necessário e depois voltam a ficar em estado inativo. O fato importante a se tratar aqui é quando eles estão no período ativo deles. Precisam ser extraordinariamente eficientes em seus manuseios de energia.

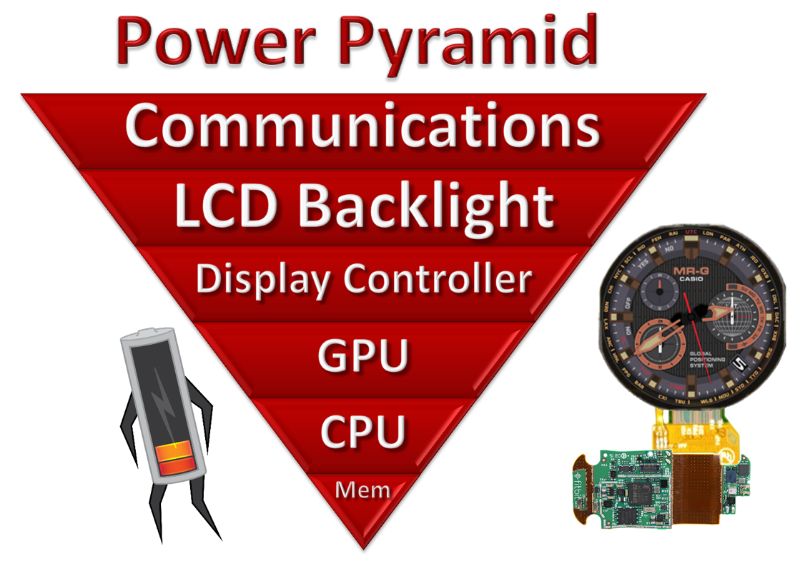

Para isso, exemplificando o sistema comunicação por meio de frequências de rádio e suas respectivas vazões, é exibido uma figura onde ilustra as respectivas frequências e os dispositivos que a utilizam.

Partindo do pressuposto que um SoC não utilizará de altas vazões para envio de dados, analisaremos primeiramente a banda à direita, chamada Narrowband IoT. Esta utiliza de forma inteligente a banda de comunicação de baixa vazão para lidar com mercados de rede ampla de baixa potência, ideal para wearables.

Também é possível perceber que, caso não possa esta banda não possa ser utilizada ou que a aplicação não suporte a vazão desta tecnologia, também seria viável o uso do LTE-M. Assim, existe inúmeras possibilidades de prover comunicação com um dispositivo mobile sem fio. Exemplo disso é a utilização do Bluetooth Low Energy (BLE), WiFi de baixo consumo (HaLow – 802.11ah) e receptores GPS de baixo consumo farão que o projeto tenha bons resultados no gerenciamento de energia.

Tensão Escalar Adaptável Em Sub-Microsegundo Em Um RISC-V De 28 Nanômetros

Princípio Da Tecnologia Apresentada No SoC Risc-V

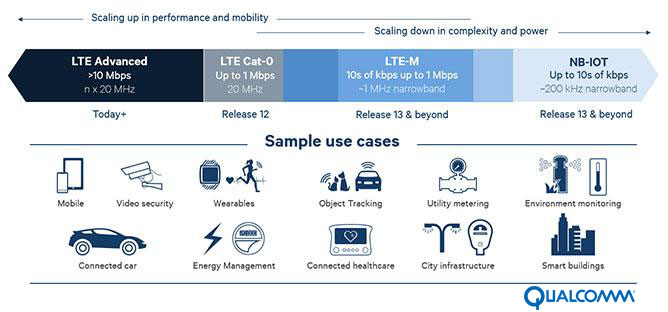

Sabendo-se então da necessidade de economia de energia em um sistema embarcado, o escalador de tensão adaptável (adaptive voltage scaling, AVS) rápido permite economizar mais energia. Um exemplo de seu funcionamento é exibido a seguir.

É possível ver no primeiro gráfico que a energia posta para realizar alguma atividade possui o ascensão e declínio lentos e após terminar uma atividade que necessita de muita energia, o decaimento do suprimento de energia segue lento, mesmo sem atividades pesadas, perdendo eficiência energética, o que ocorre diferente do segundo gráfico. Nele, é possível ver que a energia é injetada de forma gradual à atividade que será executada. Possui comportamento bem adaptável à situação, não gastando energia onde não é necessário.

Chips atuais não permitem essa configuração fina pois eles utilizam reguladores que ficam externos ao sistema, assim, quando se possui conversão fora ao sistema, existe transições lentas, poucos domínios de tensões elétricas e seu custo em integrá-lo ao sistema. Utilizando esse componente no próprio circuito interno, tem-se rápidas transições, mais domínios de tensões que os comumente encontrados hoje e a não necessidade de chips externos. O projeto a ser apresentado aqui apresenta reguladores de tensão on-chip além de um gerenciador de energia integrado para o AVS.

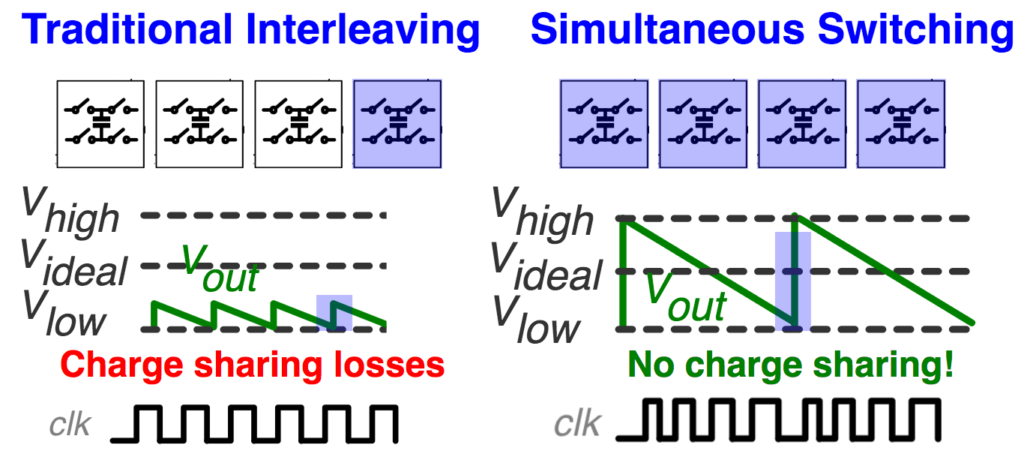

Enquanto sistemas tradicionais realizam a comutação das portas em uma de cada vez, existindo ainda a possibilidade de compartilharem atrasos nas aberturas (e fechamentos) o que não ocorre no sistema apresentado. Ele comuta cada chave simultaneamente criando assim um salto grande na tensão e sem perdas ou atrasos. Ainda também possui frequências de clock adaptadas à sua pista onduladas. Como é exibido no exemplo acima, taxa de frequências menores possuem clocks mais longos.

Núcleo De Aplicação Do SoC Risc-V

Rocket Chip Generator Do SoC Risc-V

É um gerador open-source de sistemas com cores em ordem que implementam variações do RISC-V ISA. É um projeto altamente “parameterizável” para gerar vários tipos de designs possíveis a abranger a maior quantidade de projetos possível.

O projeto baseia-se no Rocket, versão de 2014 onde possui 5 estágios em ordem baseando na implementação do RV64G.

Hwacha

Acelerador vetorial implementado por meio de instruções customizadas do ISA Hwacha que é uma extensão não padrão do projeto RISC-V, disponível em http://hwacha.org/.

É acoplado ao Rocket via interface RoCC.

Unidade De Gerenciamento De Energia Do SoC Risc-V

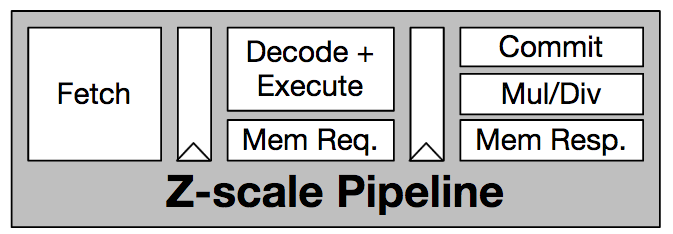

Tal unidade chama-se Z-scale. É um processador baseado em um RISC-V de pequeno porte sendo este o RV32IM. Possui pipeline de 3 estágios. Um diagrama simples de seu pipeline é exibido abaixo.

Resultados Esperados Com A Adoção Do Sistema SoC Risc-V

Utilizando toda a tecnologia citada acima, é possível ter um SoC RISC-V de 23 nanômetros com grande eficiência energética sendo algumas principais:

- Cerca de 82 a 89% de eficiência usando o clock adaptativo;

- Processador para aplicações de alta performance;

- Gerenciador de energia integrado ao sistema;

- Tensão Escalar Adaptativa em sub-microsegundos salvando mais de 40% de energia;

Article Name – SoC, Energia e RISC-V – Description – SoC RISC-V e soluções para gasto energético.

Author – Rodolfo Labiapari Mansur

Publisher Name – Laboratório iMobilis

Referência:http://www2.decom.ufop.br/imobilis/soc-risc-v-e-energia/